Our goal

This programme aims to open up new vectors of progress seeking to bring the cost of AI hardware down by >1000x.

We see an opportunity to draw inspiration from natural processing systems, which innately process information orders of magnitude more efficiently than today's largest AI systems.

If we can unlock new pathways, it will alleviate dependence on leading-edge chip manufacturing, improve access to a critical technology, and catalyse economic growth in a rapidly growing industry which is already worth trillions of pounds.

Programme structure

The programme consists of two core arms: research and development, and the Scaling Inference Lab.

Research and development

The research in this programme is split into three pillars, each with its own distinct objectives:

Charting the Course

Developing software simulators to help the research community map the expected performance/power/cost for any future combination of algorithm, hardware, componentry, and system scale.

Advanced Networking and Interconnect

We know the movement of data has become as critical as raw computational power, so we’re funding two projects to interrogate system-level and advanced network design opportunities.

New Computational Primitives

Developing new technologies with the potential to open up new vectors of progress for the field of computing, with a targeted relevance for modern AI algorithms.

Scaling Inference Lab

In an expansion of the programme, we are committing £50m to the creation of the Scaling Inference Lab: an open AI testbed designed to increase the ability of startups and other innovation engines to test new compute technologies with the goal of rapid system-level deployment and cost reduction.

Explore the R&D Creators

We're funding a portfolio of teams bringing expertise across three critical technology domains and a strong institutional mix.

Meet the Programme Director

Suraj Bramhavar

Suraj is an electrical engineer. His work focuses on how we can redefine the way computers process information to build dramatically more efficient computers. Suraj joined ARIA from Sync Computing, where he was co-founder and CTO, which optimises the use of modern cloud computing resources.

Join the team

We're hiring a Science + Technology Lead – AI Hardware Systems. In this role you will have the rare chance to catalyse breakthroughs that could change the world. You’ll be exposed to every aspect of the Scaling Compute programme's technical management from design through approval, project selection, and delivery.

Featured insights

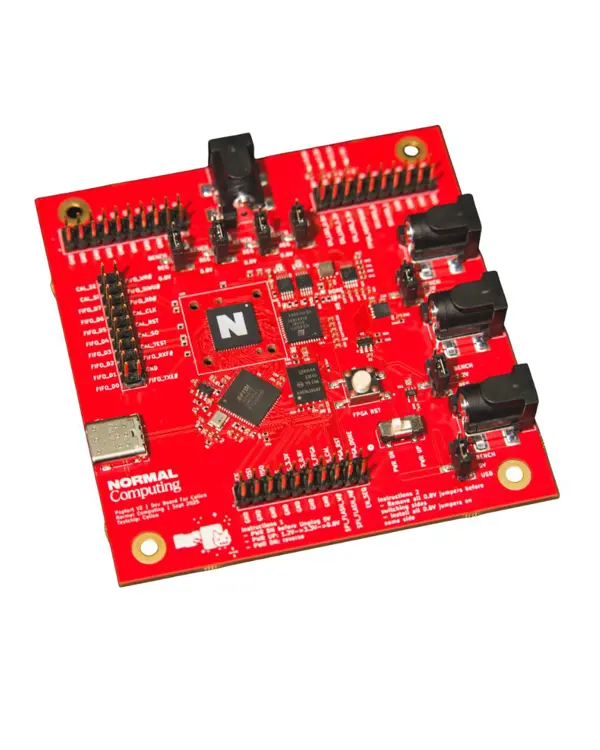

Developing a world-first thermodynamic computing chip

ARIA Substack

Normal Computing's Thermodynamic Matrix Inversion project is exploring how we can harness the laws of physics to create a new class of computer chips, so-called ‘thermodynamic’ computer chips, with the aim of making radically more efficient computers.

Sign up for updates

Stay up-to-date on our opportunity spaces and programmes, be the first to know about our funding calls and get the latest news from ARIA.