Scaling Compute

Backed by nearly £50m, this programme looks to redefine our current compute paradigm.

Our goal

To increase + open up new vectors of progress in the field of computing by bringing the cost of AI hardware down by >1000x

Why this programme

Our current mechanisms for training AI systems utilise a narrow set of algorithms and hardware building blocks, which require significant capital to develop and manufacture. The combination of this significance and scarcity has far-reaching economic, geopolitical, and societal implications.

What we’re shooting for

We see an opportunity to draw inspiration from natural processing systems, which innately process complex information more efficiently (on several orders of magnitude) than today's largest AI systems.

Unlocking a new technological lever for next-generation AI hardware, alleviating dependence on leading-edge chip manufacturing, and opening up new avenues to scale AI hardware – an industry which is worth trillions of pounds.

"Modern AI algorithms offer an opportunity to exploit principles found in nature to dramatically reduce the cost of the underlying computational hardware. If we can do this, we can fundamentally alter the existing supply chain, improve access to an increasingly important technology, and open up new use cases with massive societal benefit."

Pillars

This programme is split into four pillars, each with its own distinct objectives.

Charting the Course

Developing software simulators to help the research community map the expected performance/power/cost for any future combination of algorithm, hardware, componentry, and system scale.

Advanced Networking and Interconnect

We know the movement of data has become as critical as raw computational power, so we’re funding two projects to interrogate system-level and advanced network design opportunities.

New Computational Primitives

Developing new technologies with the potential to open up new vectors of progress for the field of computing, with a targeted relevance for modern AI algorithms.

Meet the programme team

Our Programme Directors are supported by a Programme Specialist (P-Spec) and Technical Specialist (T-Spec); this is the nucleus of each programme team. P-Specs co-ordinate and oversee the project management of their respective programmes, whilst T-Specs provide highly specialised and targeted technical expertise to support programmatic rigour.

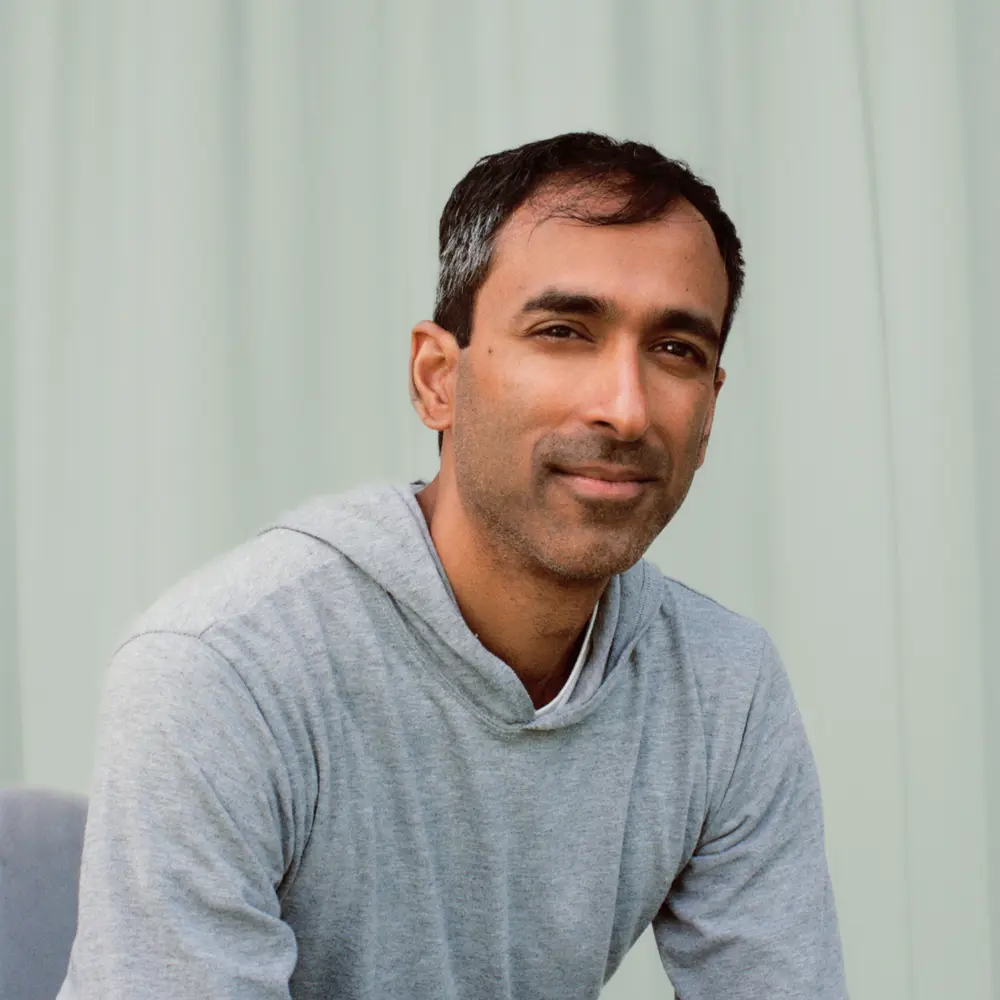

Suraj Bramhavar

Programme Director

Suraj is an electrical engineer. His work focuses on how we can redefine the way computers process information to build dramatically more efficient computers. Suraj joined ARIA from Sync Computing, where he was co-founder and CTO, which optimises the use of modern cloud computing resources.

David Stringer

Programme Specialist

David trained as a chemist at UCL before working in materials science at Imperial College London, developing nanocarbon devices for sensing, photovoltaics, and energy storage. Prior to ARIA, he built sales and operations functions at early-stage startups focusing on physics-based software for automotive and consumer electronics industries. David supports ARIA as an Operating Partner from Pace.

Paolo Toccaceli

Technical Specialist

Paolo is an electronic engineer by training, and has spent majority of his professional career in technical R&D roles for large high-tech companies, such as HP and Alcatel-Lucent. He returned to academia to earn a PhD in Machine Learning, then joined Graphcore, a startup that develops innovative AI hardware.

Featured insights

A deep dive on Scaling Compute

ARIA Substack

ARIA's Scaling Compute programme aims to revolutionize AI hardware by funding projects that explore alternative computing methods inspired by natural systems, targeting a 1000x reduction in AI hardware costs.

By uniting experts across AI systems design, mixed-signal CMOS circuits, and advanced networking, ARIA seeks to redefine current computing paradigms and alleviate dependence on leading-edge chip manufacturing. The initiative reflects ARIA's commitment to catalysing scientific progress and creating new communities and industries in the field of computing.

Sign up for updates

Stay up-to-date on our programmes and opportunity spaces.

Programme Directors

Our Programme Directors are exceptional scientists and engineers with the curiosity to explore uncharted territory

How we work

We seek out exceptional scientists and engineers and empower them with the resources and autonomy to turn their ideas into reality